Récepteur de signaux Horaires Allouis 162 Khz à PIC

Introduction

Vous trouverez ici, une nouvelle réalisation d'un récepteur de signaux horaires émis sur Allouis GO à 162 Khz (ex France Inter). Le principe de fonctionnement est identique à celui décrit sur cette page. Cependant le montage s'appuie sur une caratéristique du microprocesseur PIC 18f14k22. En effet ce circuit contient un SR Latch, c'est à dire une bascule Set et Reset, qui, utilisé en comparateur de phase, permet de remplacer le circuit CD4046 du montage précédent, rendant ainsi le montage plus compact.

Si le titre s'appuie sur le mot PIC, c'est qu'aujourd'hui, à ma connaissance, il est le seul processeur à avoir des modèles comportant un SRLatch mais tout autre processeur embarquant un SRLatch aurait le même intérêt.

Pour info, si, sur internet, vous trouvez le nom ALS162, cela concerne le sujet traité par cette page.

Réalisation

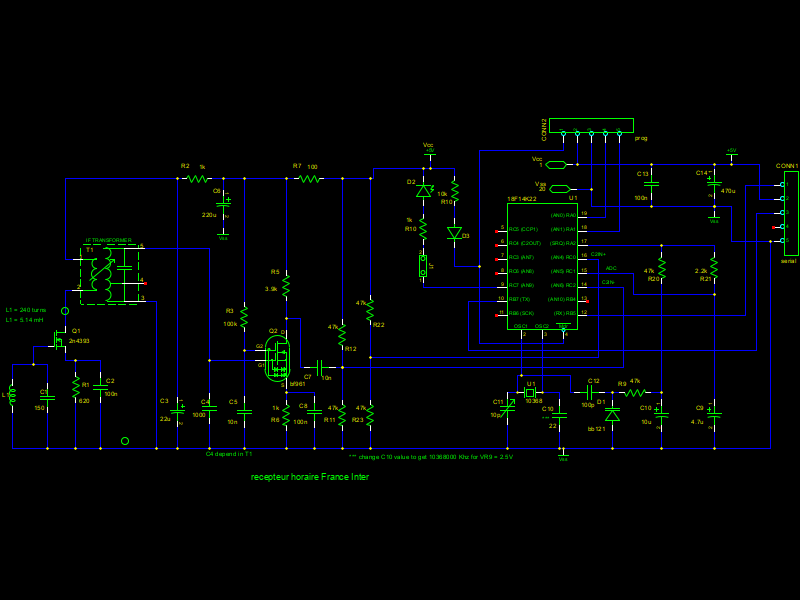

Le schéma synoptique suivant montre les composants de la boucle de phase qui constitue le matériel du récepteur. Les composants encadrés en rouge sont fournis par le processeur.

- La sortie de l'ampli d'antenne est polarisé à 2.5 V et racordée à l'entrée - du comparateur analoqique C2

- L'entrée + du comparateur analoqique C2 est polarisée à 2.5 V

- La sortie du comparateyr analoqique C2 est reliée à l'entrée Set du SRlatch

- L'oscillateur divisé par 64 est reliée à l'entrée Reset du SRlatch

- La sortie du SRlatch alimente le filtre de boucle qui pilote la varicap et le converisseur AD

- En sortie du convertisseur les données sont filtées et synchronisées sur la trame reçue

- La trame reçue peut alors être décodée par logiciel

- Les données décodées peuvent être affichées

Et voici Le schéma électrique. Cliquez pour agrandir.

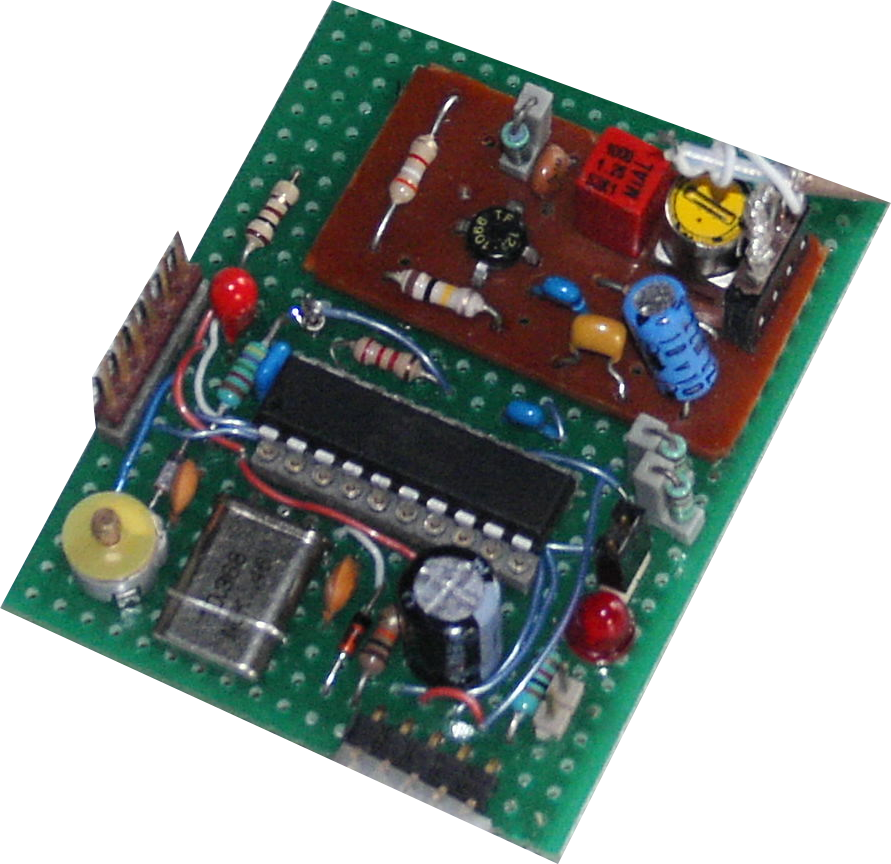

Et une photo.

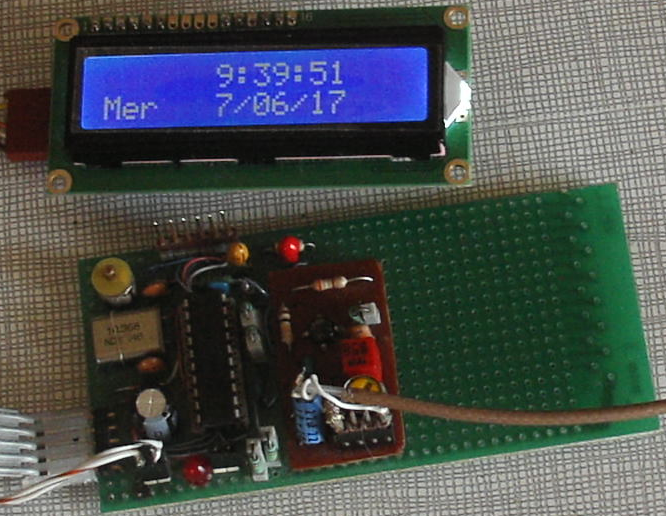

le montage émet des messgages de date et heure sur la liaison série qui peut être connectée à un affiheur.

Et une photo avec l'afficheur que vous pouvez trouver sur cette page.

La consommation du montage est de 5 mA sous 5 Volts et 20 mA avec un afficheur connecté.

Fonctionnement

L'objectif du montage est de récupérer le signal de modulation de phase transportée par l'onde émise par Allouis à 162 KHz. Pour cela on dispose du signal radio captée par l'antenne, amplifiée et de fréquence très stable et d'un signal local quasi stable, réglable en fréquence et que l'on va commencer par asservir en fréquence sur le signal reçu. C'est l'objet de la boucle de phase. Une fois asservi, le signal local devient la référence sur une entrée du comparateur de phase, l'autre entrée étant le signal reçu. Le comparateur agissant en demodulateur synchrone, on retrouve donc à la sortie une composante à la différence des fréquences et une composante à la somme des fréquences. Les 2 fréquences étant égales, on retrouve donc en bande de base le signal de modulation et un signal à la fréquence 2f qui sera éliminé par filtrage.

Le comparateur de phase est dans ce montage un SRLatch (terme de la datasheet) c'est à dire une bascule qui positionne sa sortie à 1 lors d'une impulsion sur l'entrée Set et qui positionne sa sortie à 0 lors d'une impulsion sur l'entrée Reset, avec, dans ce montage, l'oscillateur local divisé par 64 sur l'entrée Set et le signal reçu sur l'entrée Reset. La sortie est aussi positionnée à 0 lorsque les 2 entrées sont à 1. Si les signaux ont un rapport cyclique de 50 %, la tension moyenne en sortie du comparateur ne pourra varier que de 0 à Vcc/2 et est centrée sur Vcc/4. Il faudra en tenir compte pour les réglages.

L'aiguillage des signaux se fait en écrivant les valeurs adéquates (voir la datasheet) dans les registres CM2CON0, CM2CON1, SRCON0, SRCON1, VREFCON0, VREFCON1, VREFCON2.

Réglages

Vu les dispersions possible sur les quartz ou les oscillateurs, il convient de s'assurer que la plage de variation de l'oscillateur (après division) est centrée sur 162000 Hz pour une tension varicap variant de 0 à 2.5 Volt et en boucle ouverte. Au besoin modifier la valeur du condensateur sur la sortie de l'oscillateur. L'oscillateur utilisé est de type HS (High Speed voir datasheet).

La tension sur le condensateur C10 10µF varie entre 1 et 2 Volt, lorsque la boucle est accrochée.

Il est possible de sortir un signal carré à 324 kHz sur le port RC5 (CCP1) pin 5 du micro en envoyant la commande F vers l'interprêteur de commande par la liaison série.

Attention votre fréquencemètre: on doit lire 324 000.0 Hz lorsque la bouche est accrochée.

Outils

Le logiciel est développé sous Linux avec SDCC - Small Device C Compiler - voir SDCC pour le download et la documentation. La version utilisée est sdcc-src-4.3.0.tar.bz2.

SDCC utilise le paquet gputils pour gpasm et gplink, l'assembleur et le linker pour les microprocesseurs PIC. voir gputils package. La version utilisée est gputils-1.5.2.tar.xz. En général, on utilise les paquets fournis par sa distribution.

Les schémas sont réalisés avec gschem de la suite gEDA - voir [3]. Vous pourriez en avoir besoin pour modifier, imprimer, visualiser les schémas et pourquoi pas en créer d'autres.

Compilation du logiciel

Après avoir installé les outils nécessaires et rendu accessible par la modification de la variable PATH, vous pouvez exécuter les commandes suivantes:

export PATH="${PATH}:/home6/pic/gputils/bin/:/home6/pic/sdcc/bin/"

tar Jxvf picfi-yyyymmdd.tar.xz cd picfi-yyyymmdd make

Programmation du PIC

La première fois, car il y a toujours une première fois mais il peut y en avoir plusieurs, la programmation se fait par un outil ICSP (in circuit serial programming) et Pgrm le fait pour les PIC que j'utilise.

Ensuite Pgrm, connecté par la liaison série, permet le chargement du logiciel que l'on vient de modifier et recompiler. Il permet également de lire et modifier les variables internes du programme et le registres du micro.

References

- [1] Récepteur Horaire France Inter.

- [2] An Pic Avr bootloader program.

- [3] my gEDA symbols.

- [4] you can find the datasheet of the 18f14k24 processor on the Microchip Site.

LICENSE

The Picfi software is licensed under the terms of the GNU General Public License as published by the Free Software Foundation. See the file "COPYING" in the download directory.

L'utilisation du contenu présenté sur ce site est encouragée à titre personnel et à des fins d'éducation. Toute utilisation commerciale devra être soumise à une autorisation préalable.

Download

Conclusion

Démarré depuis plusieurs années et oublié parce qu'il ne fonctionnait pas correctement, ce projet a été re-sorti car il permet de fournir une fréquence 162 * 2 Khz synchronisée sur le 162 KHz sans perturber la réception. Je pensais que la cause était le manque de sensibilité du détecteur de phase par rapport au circuit 74HC4046. La cause était une mauvaise polarisation du comparateur analoghe C2, voir le schéma. Avec ces modification, la synchronisation est devenue plus stables.

Il est donc possible de réaliser une boucle à verrouillage de phase matérielle avec les composants internes du microprocesseur. Les connections (inisibles) sont réalisées en positionnant des bits dans les registres. Il est nécessaire d'avoir la datasheet sous les yeux !.