Récepteur Horaire France Inter

L'émission de la station de radio France Inter sur les grandes ondes à 162 kHz en modulation d'amplitude s'est arrêtée le 1 janvier 2017. Cette page est relative à la réception des signaux horaires en modulation de phase de ce même émetteur qui continue son émission et est, en conséquence, toujours d'actualité...

L'émetteur est en maintenance tous les mardi matin de 8 H à midi. Eviter de faire des essais pendant ces heures !

Introduction

Ce récepteur Horaire France Inter est un petit montage électronique comprenant un microprocesseur et un récepteur radio qui permet de recevoir les signaux horaires émit par l'émetteur de France Inter en Grandes Ondes ( GO ) à la fréquence de 162 Khz. Ces signaux sont insérés sur la porteuse par une modulation de phase en plus de la modulation d'amplitude qui, elle, porte l'émission radiophonique que tout le monde connait.

Si on regarde les articles traitant la réception de signaux horaires en général, on constate que tous, sauf un [2], concernent la réception de DCF77 et que la majorité de ceux-ci utilisent un module intégré pour la partie réception, un microprocesseur pour le décodage. On pourrait s'étonner du manque d'intérêt pour la réception de France Inter, sans doute expliqué par la complexité supposée de la détection de phase. En fait, il n'en est rien et c'est ce que veut monter cet article.

Implémentation

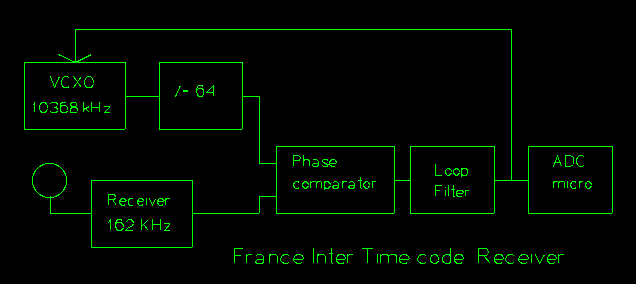

L'article [1] explique le principe utilisé pour le codage des signaux horaires sur France Inter. Il indique, aussi, les ingrédients nécessaires à la détection d'un signal modulé en phase comme celui émis par France Inter :

- un oscillateur piloté par quartz de type VCXO.

- une boucle à verrouillage de phase.

- un microprocesseur pour le décodage de la trame.

Or dans un montage à microprocesseur, nous avons déjà à notre disposition un oscillateur à quartz et si on y ajoute une varicap, il devient VCXO. On dispose également du diviseur nécessaire à la boucle de phase.

Les contraintes de choix du quartz sont:

- fréquence multiple pair de 162 Khz.

- fréquence entre 5 et 15 Mhz.

- disponibilité chez un fournisseur.

Après recherche, la fréquence est choisie à 10368 Khz, soit 64 * 162 Khz. Le quartz est disponible chez ce fournisseur [3].

La boucle à verrouillage de phase est constitué d'un comparateur de phase, le circuit intégré cmos CD4046, dont la sortie est connectée, à travers le filtre de boucle, à la varicap du VCXO ainsi qu'à une des entrées convertisseur analogique/numérique CAD du microprocesseur, un AVR Atmega8 de chez Atmel. Une entrée du comparateur est reliée à la sortie timer/counter 2 du microprocesseur. L'entrée signal du comparateur est reliée à la sortie du récepteur.

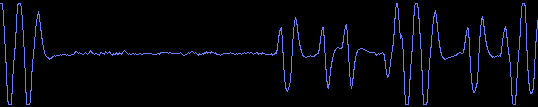

En principe, dans une boucle à verrouillage de phase, on cherche à minimiser l'erreur en sortie du comparateur grâce à un gain de boucle élevé et un filtre d'ordre 2 ou 3. Ici au contraire, à partir du moment où on se place dans les conditions de verrouillage en fréquence, on cherche à maximiser l'erreur puisque c'est ce que l'on veut mesurer. Le gain du VCXO est faible quelques +- 5 Hz * 64 par rapport à sa fréquence centrale, pour une variation de 0 à 5 Volts sur l'entrée varicap. Le filtre de boucle, du premier ordre, est réalisé par un simple réseau RC. En sortie du filtre les fréquences élevées étant éliminées, il reste une tension continue et en superposition une tension alternative représentant la modulation de phase. C'est ce signal que voit le convertisseur analogique/numérique du microprocesseur. L'image, ci-dessous, montre l'allure d'une toute petite fraction ( environ 2 secondes ) du signal au moment du top de synchro à la 59 ième seconde de la trame. C'est de ce signal qu'il va falloir extraire les informations horaires.

Le récepteur est un modèle à amplification directe. En effet il n'y a que la fréquence de 162 Khz à sélectionner et à amplifier, il n'y a donc pas besoin du changement de fréquence traditionnel. L'antenne active est constituée d'un circuit accordé à 162 Khz monté sur un barreau de ferrite et d'un transistor FET. Cette disposition permet l'éloignement de l'antenne du récepteur si le bruit ambiant ( bruit de PC par exemple) gêne la réception. Un niveau de 250 mVolt en sortie de l'ampli est suffisant pour attaquer le comparateur qui dispose d'un amplificateur sur son entrée signal.

Principe du décodage

Le principe du décodage du signal horaire s'articule autour de 3 fonctions :

- le détecteur.

- le séquenceur.

- le décodeur de trame.

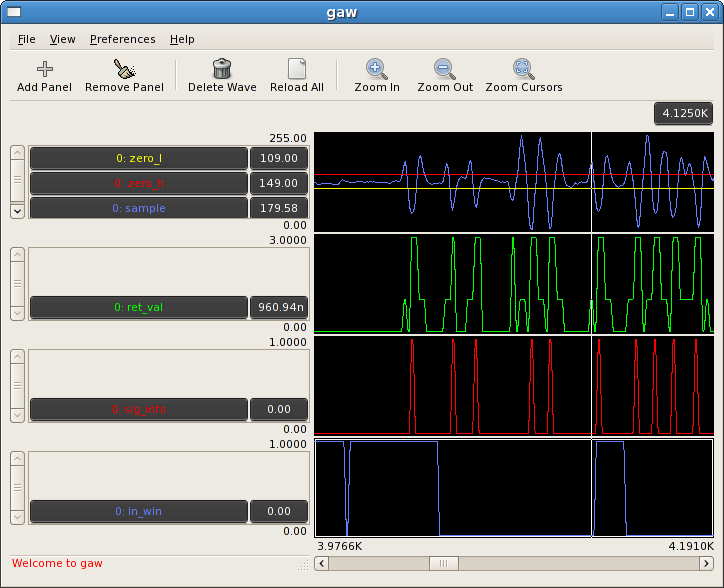

Le détecteur reçoit le signal indiqué dans la 1 ière fenêtre de l'image ci-dessous. C'est le signal que fournit le convertisseur analoqique digital. On commence par se fixer un seuil de part et d'autre de la valeur moyenne du signal. On donne ensuite à une variable ret_val la valeur 0, si le signal se trouve entre les 2 seuils, 1 si il se trouve au dessus et 3 si on se trouve en dessous. C'est le signal de la deuxième fenêtre. Une 2 ième variable sig_info est positionée à 1 si la valeur courante de val_val est à 3 et ( ret_val = 1 à t-1 ou (ret_val = 0 à t-1 et ret_val = 1 à t-2)) et sinon elle est à 0. Autrement dit, on détecte une transition négative. C'est le signal de la 3 ième fenêtre, et celui que reçoit le séquenceur. Ce traitement n'est rien d'autre qu'un filtrage numérique.

Le séquenceur a pour rôle de rechercher la synchronisation, de la conserver et lire la valeur du bit qui se présente pour la stocker jusqu'à réception complète d'une trame. Pour cela, il établit un signal in_win actif à 1 d'une durée de 200 ms, répété toutes les secondes et calé sur le bit 0 de la trame, c'est à dire le premier bit après le top de synchro. Celui-ci apparait à la 59 ième seconde et se caractérise par l'absence d'impulsion pendant au moins 1 seconde. La 4 ième fenêtre montre le signal in_win. La valeur donnée du bit reçu est 1 si il y a 2 impulsions du signal sig_info dans la fenêtre in_win et 0 sinon. Sur l'image, les 2 premiers bits ont pour valeur 0.

La trame étant complète à la 59 ième seconde, le décodeur transforme les champs de bits de cette trame en valeurs binaires plus exploitables par un programme, et les stocke dans une structure dont les champs sont : le jour, le mois, l'année, l'heure, les minutes, les secondes, le numéro de jour dans la semaine, le décalage horaire par rapport à GMT. Les infos sont alors utilisables et peuvent, par exemple, être envoyées vers un afficheur. Pour toutes les infos sur le codage de la trame voir [1]. Le module décodeur peut aussi décoder DCF77.

Les informations de l'image suivante sont fournies par un programme tournant sur PC dont l'entrée, carte son, est connecté (uniquement pour essai) à l'entrée CAN du micro. Ce programme fournit aussi, bien sûr l'heure. Avec cette connexion, la radio est audible en prime !.

Il peut être utile de noter que des informations, autre que les signaux horaires, sont présentes dans le signal recu.

Hardware

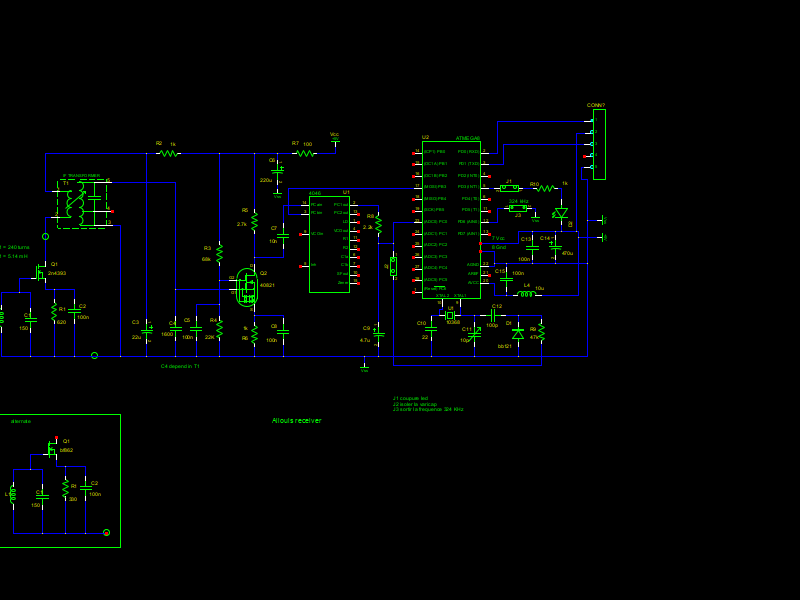

Le paragraphe sur l'implémentation a déjà bien introduit les composants. Il reste à visualiser le schéma que voici:

On peut préciser que le montage fonctionne sous 5 Volts et consomme environ 20 mA.

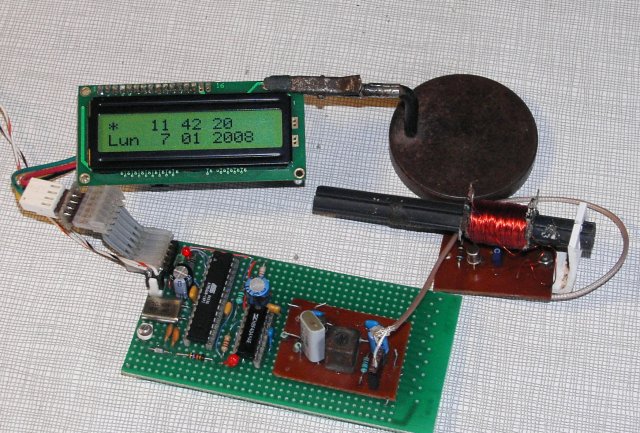

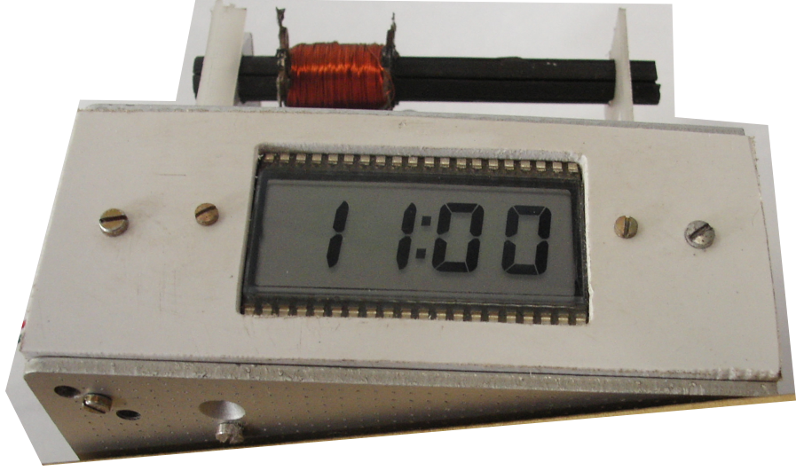

Une photo du montage: c'est encore expérimental !.

Remarquez la précision du fréquenecemètre ! ... après, bien sur, le réglage de son oscillateur.

le microprocesseur

Le microprocesseur utilisé est un atmega8 [4] de la série AVR Atmel dont l'intérêt essentiel est la mémoire programme de type flash sans quoi le développement serait impossible sans outil onéreux. Il permet l'écriture du programme directement en language C. Il peut se programmer lui-même sur le montage par l'intermédiaire d'un de ses périphériques après avoir installer un programme de boot dans la partie haute de la mémoire flash.

Software

Le logiciel est écrit en C et s'appuie sur la librairie Avr libc ainsi que sur le compilateur avr-gcc de la suite gcc.

Comme dans tout logiciel, on commence par une phase d'initialisation des périphériques:

- le convertisseur analogique numérique

- le timer 0.

- le timer 1.

- le timer 2.

- l'uart.

Le convertisseur analogique numérique est initialisé pour sélectionner l'entrée 0, travailler sur 8 bits avec une référence de Avcc.

Le timer 0 sert , habituellement, de référence de temps interne. Une interruption intervient à une fréquence d'environ 100Hz. Mais dans ce montage, le timer ne disposant que de 8 bits ne peut fournir la référence souhaitée. Il reste cependant actif pour le témoin d'activité et le reset du Watchdog.

Le timer 1 est initialisé pour diviser la fréquence du quartz par 8 * 12960 et fournir une fréquence d'interruption de 100 Hz soit tous les 10 ms et qui incrémente un compteur référence de temps à chaque interruption. Le CAD est donc lu à cette cadence puis l'échantillonage relancé. Cependant 1 seul échantillon sur 2 participe à l'élaboration du signal précédemment appelé sig_info, dans ce document. Les échantillons sont aussi utilisés pour la création des niveaux de seuil, dont on a également parlé. En effet la valeur moyenne du signal varie pour compenser les dérives éventuelles de l'oscillateur , par exemple avec la température. Il faut donc la mesurer pour faire bouger les seuils en conséquence.

Le timer 2 est initialisé pour diviser la fréquence du quartz par 64 et fournir sur la sortie OCR2 un signal carré de fréquence 162 Khz +- delta.

L'uart est initialisé pour fonctionner à un débit de 9600 bits/s. Il sert à envoyer un message d'affichage de l'heure toutes les secondes. En cours de développement il sert à communiquer avec le programme et à reprogrammer le micro pour une nouvelle version.

Après l'initialisation, le programme entre dans sa boucle principale qui est le séquenceur de réception décrit précédemment.

Ce montage dispose d'un dispositif d'affichage Lcd incorporé, en effet plusieurs port sont disponibles et permettent de connecter un afficheur lcd 2 lignes par 16 caractères et fonctionnant en interface 4 bits. Le logiciel détecte donc au démarrage la présence de cet afficheur et appele les fonctions d'affichage lorsque nécessaire en plus de l'émission sur la liaison série.

Horloge interne

La réception du signal peut être affectée et dans ce cas les informations concernant l'heure et la date sont erronées. Pour pallier à cela, une horloge interne est constamment tenue à jour par les informations issus du décodage si elles sont correctes ou sinon par division de l'interruption à 100 Hz. Dès l'apparition d'un problème de réception, elle prend le relai pour la transmission des infos vers la liason série ou l'afficheur.

Outils de développements

Le logiciel est développé sur un systeme Linux. Pour ce faire, il est nécessaire de disposer d'un compilateur spécifique pour les AVR et installer les paquets suivants, qui ne sont pas installés par défaut :

- avr-gcc.

- avr-binutils.

- avr-libc.

Les schémas sont crées avec gschem qui fait partie de la suite gEDA.

Compilation

Après installation des outils, exécuter les commandes suivantes:

tar zxvf fi-yyyymmdd.tar.xz cd fi-yyyymmdd make

Réglages

Les réglages consistent à :

- Accorder le cadre et le transfo sur 162 Khz.

- En boucle ouverte, régler le condensateur variable pour obtenir une fréquence de 162 Khz à la sortie du micro avec 2.5 v sur la varicap.

Composants spéciaux

Les composants utilisés proviennent des fonds de tiroir et peuvent s'avérer difficiles à trouver. Le montage ne comporte aucun élément critique, il n'y donc a aucune obligation technique à utiliser les références du schéma.

- Self L1 : c'est le cadre d'un récepteur radio GO.

- Transfo T1 : transfo FI de récepteur monté à l'envers. La valeur du condensateur d'accord peut varier en fonction du transfo.

- Q1 2n4393 -> BF256.

- Q2 40821 -> BF961.

- Utiliser un 74HC4046 au lieu d'un CD4046 -> plus de gain.

- On peut remplacer l'atmega8 par atmega88.

- Certains s'amusent avec atmega328...

A faire

- Réduire la consommation en utilisant un atmeg88 qui permet de diviser l'horloge système.

- Réduire le volume....

- Vérifier que la sensibilité du récepteur est suffisante partout... et rajouter un étage amplicateur si nécessaire.

- Il manque l'affichage de la température...m'a dit quelqu'un

une boite pour l'horloge

Après plusieurs années, j'ai fini par faire une boite pour loger cette horloge !

Références Documentaires

- Diffusion de l'heure par France Inter.

- Un article sur la construction d'un récepteur France Inter. ou un autre lien sur le même article

- Electronique Diffusion.

- Site de Atmel pour la datasheetdu micro.

- Pour download de Gaw.

LICENSE

The fi software is licensed under the terms of the GNU General Public License as published by the Free Software Foundation. See the file "COPYING" in the download directory.

L'utilisation du contenu présenté sur ce site est encouragée à titre personnel et à des fins d'éducation. Toute utilisation commerciale devra être soumise à une autorisation préalable.